# LZ2314J

## DESCRIPTION

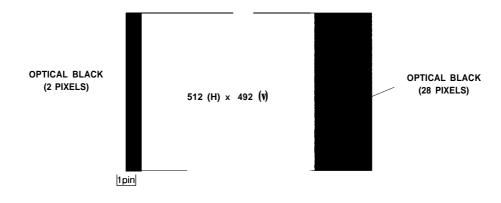

U2314J is a 1/3-type (6.0 mm) solid-state image sensor that consists of PN phote-diodes and CCDS (charge-coupled devices). Having approximately 270000 pixels (horizontal 542 x vertical 492), the sensor provides a high resolution stable B/W image,

## FEATURES

- Number of pixels : 512 (H) x 492 (V) Pixel pitch : 9.6 μm(H)×7.5 μm (V) Number of optical black pixels : Horizontal; front 2 and rear 28

- Low fixed pattern noise and lag

- No sticking and no image distortion

- Blooming suppression structure

- Built-in output amplifier

- Variable electronic shutter (1/60 to 1/10 000 s)

- Compatible with EIA standard

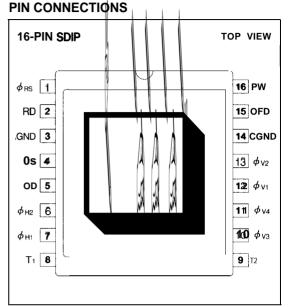

- Package : 16-pin SDIPICERDIP](WDIPO1 6-N-050( ン)

1/3 type B/W CCD Area Sensor for EIA

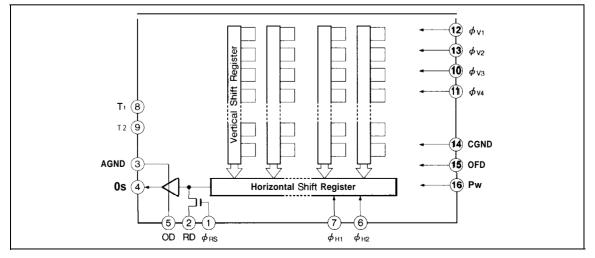

## BLOCK DIAGRAM

## PIN DESCRIPTION

| SYMBOL                                                                        | PIN NAME                             |

|-------------------------------------------------------------------------------|--------------------------------------|

| RD                                                                            | Reset transistor drain               |

| OD                                                                            | Output transistor drain              |

| Os                                                                            | Video output                         |

| φRS                                                                           | Reset transistor gate clock          |

| $\phi_{\mathrm{V1}},\phi_{\mathrm{V2}},\phi_{\mathrm{V3}},\phi_{\mathrm{V4}}$ | Vertical shift register gate clock   |

| фн1, фн2                                                                      | Horizontal shift register gate clock |

| OFD                                                                           | Overflow drain                       |

| Pw                                                                            | P type well                          |

| AGND                                                                          | Analog part ground                   |

| CGND                                                                          | Clock part ground                    |

| Т1, т2                                                                        | Test terminal                        |

# **ABSOLUTE MAXIMUM RATINGS**

|                                                  |           | ۰<br>۱           | D = LOO |

|--------------------------------------------------|-----------|------------------|---------|

| PARAMETER                                        | SYMBOL    | RATING           | UNIT    |

| Output transistor drain voltage                  | Vod       | Oto +18          | v       |

| Reset transistor drain voltage                   | Vrd       | Oto +18          | v       |

| Overflow drain voltage                           | VOFD      | • to +55         | v       |

| Test terminal, T1                                | VT1       | Oto +18          | v       |

| Test terminal, τ2                                | VT2       | -0.3 to +18      | v       |

| Reset gate clock voltage                         | V ¢ RS    | -0.3 to +18      | v       |

| Vertical shift register clock voltage            | V ¢ ∨     | -9.0 to +18      | v       |

| Horizontal shift register clock voltage          | Vøн       | -0.3 to +18      | v       |

| Voltage difference between PW and vertical clock | Vpw – Vøv | -27 to O         | v       |

| Storage temperature                              | Tstg      | -20 to +80       | °C      |

| Operating ambient, temperature                   | Topr      | $-20 t_{0} + 70$ | °C.     |

$(Ta = 25^{\circ}C)$

## **RECOMMENDED OPERATING CONDITIONS**

| PARAMETER                                 |                            | SYMBOL                               | MIN.                                 | TYP.    | MAX. | UNIT       | NOTE |   |

|-------------------------------------------|----------------------------|--------------------------------------|--------------------------------------|---------|------|------------|------|---|

| Operating ambient temperature             |                            | Topr                                 |                                      | 25,0    |      | °C         |      |   |

| Output trans                              | istor drain vo             | oltage                               | Vod                                  | 14.5    | 15.0 | 16.0       | v    |   |

| Reset transis                             | stor drain vol             | tage                                 | Vrd                                  |         | Vod  |            | v    |   |

| Overflow                                  | When DC is                 | s applied                            | Vofd                                 | 5.0     |      | 19.0       | v    | 1 |

| drain                                     | When pulse<br>p-p level    | e is applied                         | V ¢ OFD                              | 22.0    |      |            | v    | 2 |

| Analog part                               | ground                     |                                      | AGND                                 |         | 0.0  |            | v    |   |

| Clock part g                              | Clock part ground          |                                      | CGND                                 |         | 0.0  |            | v    |   |

| P-well voltage                            |                            | VPW                                  | -9.0                                 |         | Vøv∟ | v          |      |   |

| Test terminal, Tı                         |                            | <b>V</b> T1                          |                                      | Vod     |      | v          |      |   |

| Test termina                              | Test terminal, T2          |                                      | VT2                                  |         | 0,0  |            | v    |   |

| Vertical shift<br>register clock          |                            | LOW level                            | V φ V1L, V φ V2L<br>V φ V3L, V φ V4L | - 8.5   | -8.0 | -7,5       | v    |   |

|                                           | INTERMEDIATE<br>level      | V & V11, V & V21<br>V & V31, V & V41 |                                      | 0,0     |      | v          |      |   |

|                                           |                            | HIGH level                           | Vøv1h, Vøv3h                         | 16.0    | 16.5 | 17.0       | v    |   |

| Horizontal shift                          |                            | LOW level                            | VøH1L, VøH2L                         | -0.05   | 0.0  | 0.05       | v    |   |

| register clock                            | HIGH level                 | Vøh1h, Vøh2h                         | 4,7                                  | 5.0     | 6.0  | v          |      |   |

| Decet rate                                | aliali                     | LOW level                            | ν φ RSL                              | 0,0     |      | Vrd - 12.0 | v    |   |

| Reset gate clink                          | CIIIK                      | HIGH level                           | V ¢ RSH                              | VRD-7.5 |      | 9.5        | v    |   |

| Vertical shift register clock frequency   |                            | føv1, føv2<br>føv3, føv4             |                                      | 15.73   |      | kHz        |      |   |

| Horizontal shift register clock frequency |                            | føhi, føh2                           |                                      | 9.53    |      | MHz        |      |   |

| Reset gate                                | Reset gate clock frequency |                                      | føRS                                 |         | 9.53 |            | MHz  |   |

NOTES :

1. When DC voltage is applied, shutter speed is 1 /60 seconds.

2. When pulse is applied, shutter spaed is less than 1/60 seconds.

## ELECTRICAL CHARACTERISTICS (Drive method : Field Accumulation)

(Ta=  $25^{\circ}$ C, Operating conditions : typical values for the recommended operating conditions, Color temperature of light source : 3200 K / IR cut-off filter (CM-500, 1 mmt))

| PARAMETER                       | SYMBOL | MIN. | TYP.  | MAX.  | UNIT | NOTE |

|---------------------------------|--------|------|-------|-------|------|------|

| Photo response non-uniformity   | PRNU   |      |       | 10    | %    | 2    |

| Saturation signal               | Vsat   | 500  |       |       | mV   | 3    |

| Dark output voltage             | Vdark  |      | 0.3   | 3.0   | mV   | 1, 4 |

| Dark signal non-uniformity      | DSNU   |      | 0.6   | 2.0   | mV   | 1, 5 |

| Sensitivity                     | R      | 240  | 360   |       | mV   | 6    |

| Gamma                           | Y      |      | 1     |       |      |      |

| Smear ratio                     | SMR    |      | 0.009 | 0,016 | %    | 7    |

| Image lag                       | AI     |      |       | 1.0   | %    | 8    |

| Blooming suppression ratio      | ABL    | 1000 |       |       |      | 9    |

| Output transistor drain current | lod    |      | 4.0   | 6.0   | mA   |      |

| Output impedance                | Ro     |      | 300   |       | Ω    |      |

| Dark noise                      | Vnoise |      | 0,2   | 0.4   | mV   | 10   |

| OB difference in level          |        |      |       | 1,0   | mV   | 11   |

- The standard output voltage is defined as 150 mV by the average output voltage under uniform illumination.

- The standard exposure level is defined when the average output voltage is 150 mV under uniform illumination.

#### NOTES :

- 1. Ta : +60°C

- 2. The image area is divided into 10X 10 segments. The segment's voltage is the average output voltage of all the pixels within the segment. PRNU is defined by (Vmax Vmin)/Vo, where Vmax and Vmin are the maximum and the minimum values of each segment's voltage respectively, when the average output voltage Vo is 150 mV.

- 3 The image area is divided into 10X 10 segments. The saturation signal is defined as the minimum of each segment's voltage which is the average output voltage of allthe pixels within the segment, when the exposure level is set as 10 times, compared to standard level.

- 4 The average output voltage under a non-exposure condition.

- 5 The image area is divided into 10X 10 segments. DSNU is defined by (Vdmax – Vdmin) under the non-exposure condition where Vdmax and Vdmin are the maximum and the minimum values of each segment's voltage, respectively,

that is the average output voltage over all pixels in the segment.

- The average output voltage when a 1 000 lux light source attached with a 90% reflector is imaged by a lens of F4, f50 mm.

- 7. The sensor is adjusted to position a V/I O square at the center of image area where V is the vertical length of the image area. SMR is defined by the ratio of the output voltage detected during the vertical blanking period to the maximum of the pixel voltage in the V/I O square.

- 8. The sensor is exposed at the exposure level corresoonding to the standard condition preceding non-exposure condition. Al is defined by the ratio between the output voltage measured at the 1st field during the non-exposure period and the standard output voltage.

- 9 The sensor is adjusted to position a V/I O square at the center of image area. ABL is the ratio between the exposure at the standard condition and the exposure at a point where a blooming is observed.

- 10 The RMS value of the dark noise (after CDS). The bandwidth range is from 1 00 kHz to 4.2 MHz.

- 11 The difference between the average output voltage of the effective area and the OB part under the non-exposure condition.

# PIXEL STRUCTURE

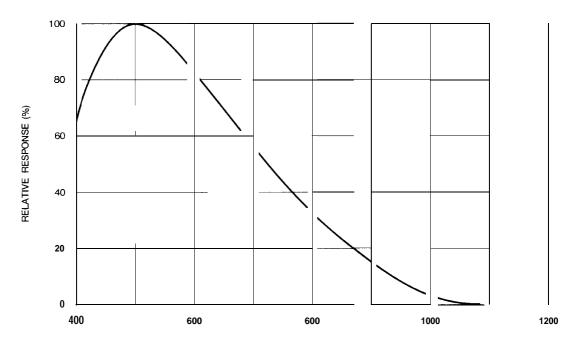

## SPECTRAL RESPONSE EXAMPLE

WAVE LENGTH (rim)

## SHARP

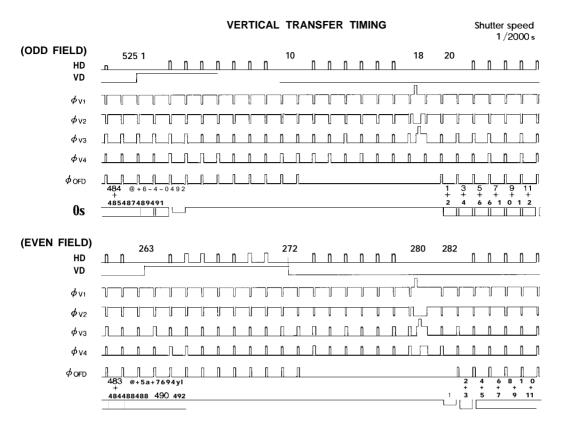

## TIMING DIAGRAM EXAMPLE

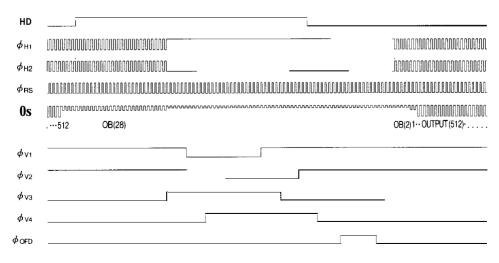

#### HORIZONTAL TRANSFER TIMING

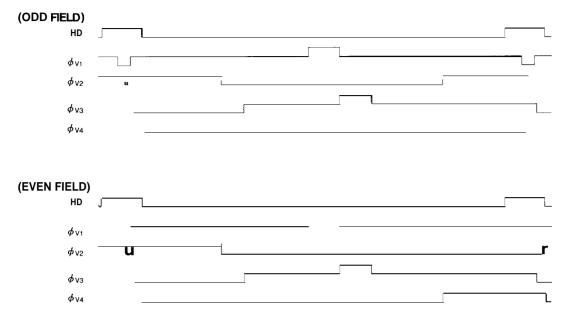

## READOUT TIMING

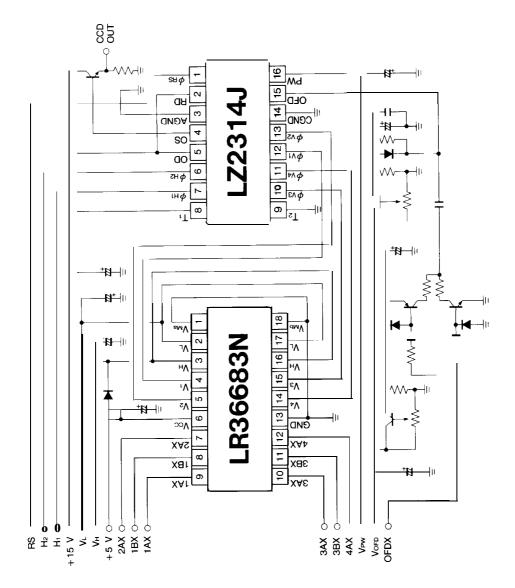

# SYSTEM CONFIGURATION EXAMPLE